ዝርዝር ሁኔታ:

- ደረጃ 1: ስርዓት ጥቁር ሣጥን

- ደረጃ 2: አካላት

- ደረጃ 3: D Flip-Flops

- ደረጃ 4 - ሁኔታዎች

- ደረጃ 5: ገደቦች

- ደረጃ 6 ዋና ምንጭ ፋይል

- ደረጃ 7 - ስብሰባ

- ደረጃ 8 - ፕሮግራሙን በመጫን ላይ

ቪዲዮ: ኃይል ቆጣቢ እንቅስቃሴ የነቃ የመንገድ መብራቶች 8 ደረጃዎች

2024 ደራሲ ደራሲ: John Day | [email protected]. ለመጨረሻ ጊዜ የተሻሻለው: 2024-01-30 07:31

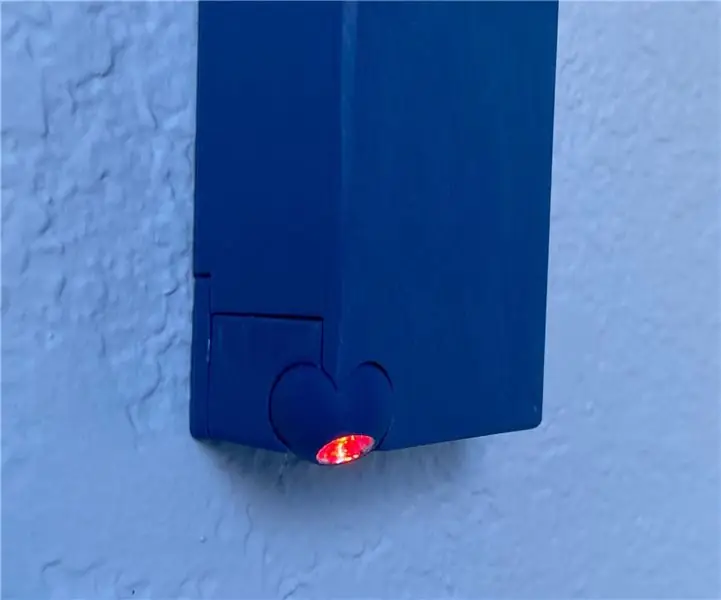

በዚህ ፕሮጀክት ግባችን ማህበረሰቦችን ኃይል እና የገንዘብ ሀብቶችን የሚያድን አንድ ነገር መፍጠር ነበር። በእንቅስቃሴ የተንቀሳቀሱ የመንገድ መብራቶች ሁለቱንም ነገሮች ያደርጉ ነበር። በመላ አገሪቱ ኃይል ባዶ ጎዳናዎችን በማብራት የመንገድ መብራቶች ላይ ይባክናል። የመንገድ መብራት ስርዓታችን ስፍር ቁጥር የሌላቸው ዶላሮችን በማዳን መብራቶች አስፈላጊ ሲሆኑ ብቻ መብራታቸውን ያረጋግጣል። የእንቅስቃሴ ዳሳሾችን በመጠቀም ስርዓቱ መብራቶችን ያበራል መኪናዎች ሲገኙ ብቻ። እንዲሁም ለእግረኞች ደህንነት በመንገድ ላይ ያሉትን ሁሉንም መብራቶች የሚያበራ የማሻገሪያ ቁልፍን ተግባራዊ እናደርጋለን። የሚከተሉት ደረጃዎች ቪቫዶን እና ባሲስ 3 ቦርድን በመጠቀም የፕሮጀክቱን የመቀነስ ሞዴል እንዴት እንደሠራን እና እንደገነባን ይራመዱዎታል።

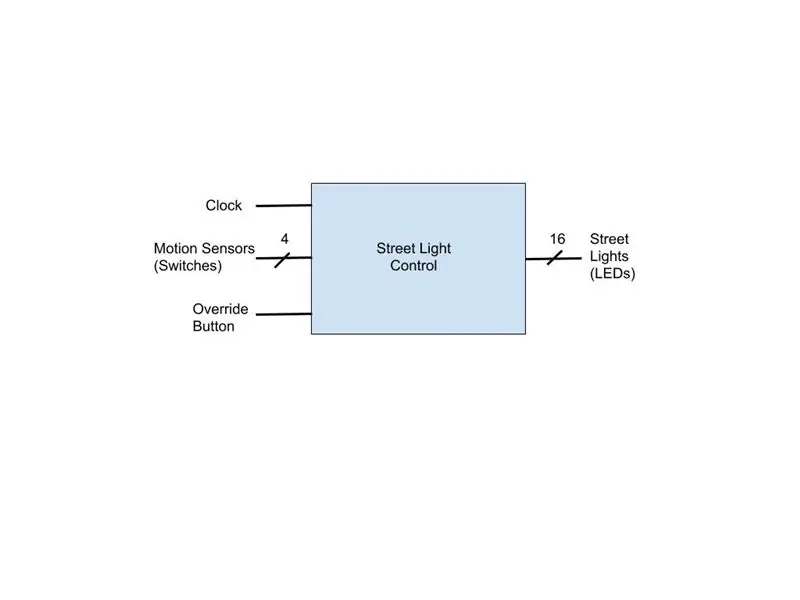

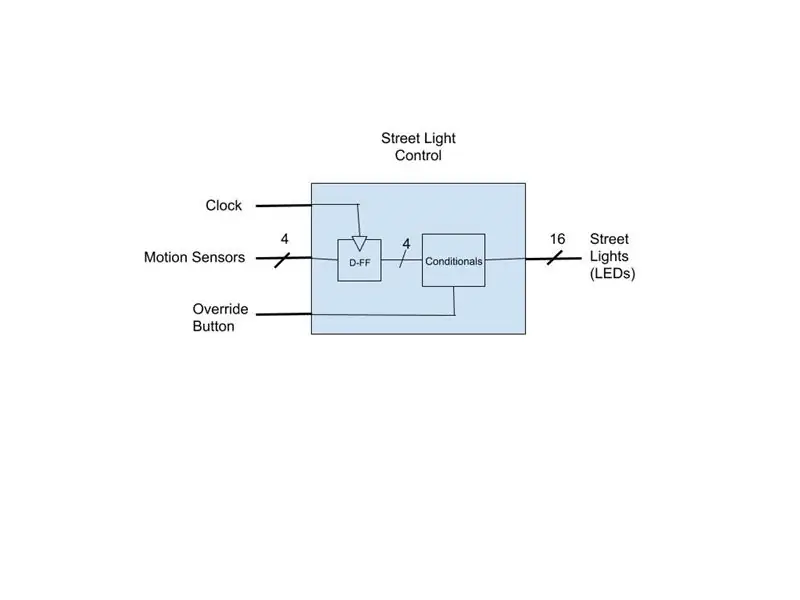

ደረጃ 1: ስርዓት ጥቁር ሣጥን

ይህንን ፕሮጀክት የጀመርነው ቀለል ያለ የጥቁር ሣጥን ንድፍ በመሳል ነው። የጥቁር ሣጥን ሥዕላዊ መግለጫ ሥርዓታችን ሁሉንም አስፈላጊ ሂደቶች ለማጠናቀቅ የሚፈልገውን ግብዓቶች እና ውጤቶች ያሳያል። የእኛን ንድፍ በተቻለ መጠን ቀላል እና መሠረታዊ ለማድረግ ሞክረናል። ሦስቱ የሥርዓት ግብዓቶቻችን አውቶቡስ የእንቅስቃሴ ዳሳሾች (4 ለዝቅተኛ ሞዴላችን) ፣ የእግረኛ መሻገሪያ ቁልፍ እና የሰዓት ግብዓት አካተዋል። በሌላ በኩል የእኛ ነጠላ ውጤት የመንገድ መብራቶቻችንን የሚወክል የ LED መብራቶች አውቶቡስ ነው። ለዚህ ሞዴል በ Basys 3 ሰሌዳ ላይ በ LED ውጤቶች ውስጥ የተገነቡት ከፍተኛው ቁጥር ብቻ ስለሆነ የ 16 የመንገድ መብራቶችን ሁኔታ ተጠቀምን። በመጨረሻም ፣ ይህንን ሥዕላዊ መግለጫ በመጠቀም የቪቫዶ ፕሮጄክታችንን ፣ ምንጩን እና ውስን ፋይሎችን በተገቢው ግብዓቶች እና ግብዓቶች መፍጠር ችለናል።

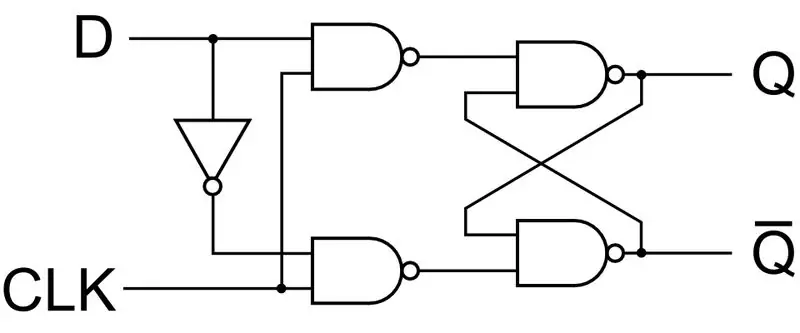

ደረጃ 2: አካላት

በዚህ ደረጃ የጥቁር ሣጥን ዲያግራማችንን የሠሩትን ክፍሎች በጥልቀት እንመረምርበታለን። የእኛ የመጀመሪያ ክፍል ዲ flip-flops የያዘ የ VHDL ምንጭ ፋይል ነው። D Flip-flops በሰዓት መነሳት ጠርዝ ላይ ከሚገኙት ዳሳሾች የሚመነጨውን ማንኛውንም ምልክት በቀላሉ ይወስዳል እና ያንን መረጃ እስከሚቀጥለው ከፍ ወዳለው ጠርዝ ድረስ ያቆየዋል። ይህ የእኛን ስሱ የእንቅስቃሴ ዳሳሾች የውጤት LED ን ከ “ብልጭ ድርግም” እንዳያመጡ ያደርጋቸዋል። እንዲሁም ፣ አዝራሩ ከተገፋ በኋላ ኤልኢዲውን ለ 5-7 ሰከንዶች ያህል ለማቆየት በአዝራሩ የግቤት ምልክት ላይ አንድ ነጠላ D Flip-flop ን እናስቀምጣለን። እኛም ይህንን በሰዓት መከፋፈያ በኩል አሂደናል።

አካል clk_div2 ወደብ ነው (clk: std_logic ውስጥ; sclk: out std_logic); መጨረሻ clk_div2;

የ clk_div2 ሥነ ሕንፃ my_clk_div ነው

ቋሚ max_count: ኢንቲጀር = = (300000000); ምልክት tmp_clk: std_logic = '0'; my_div: ሂደት (clk ፣ tmp_clk) ተለዋዋጭ div_cnt: ኢንቲጀር = 0; ከሆነ (የሚነሳው_ገደል (clk)) ከዚያ ከሆነ (div_cnt = MAX_COUNT) ከዚያ tmp_clk <= tmp_clk አይደለም ፤ div_cnt: = 0; ሌላ div_cnt: = div_cnt + 1; ከሆነ ያበቃል; ከሆነ ያበቃል; sclk <= tmp_clk; የማጠናቀቂያ ሂደት my_div; የእኔ_clk_div ጨርስ;

በዚህ ሥዕላዊ መግለጫ ውስጥ የእኛ የመጨረሻው ክፍል የግብዓት ምልክቶች ውቅረትን መሠረት በማድረግ ለውጦቹ ሁኔታዎችን የሚያካትት የባህሪ VHDL ምንጭ ፋይል ነው።

ደረጃ 3: D Flip-Flops

በግብዓት ምልክቶች ላይ የተጣበቁት አራቱ ተንሸራታቾች ለሥርዓታችን ተግባራዊነት አስፈላጊ ናቸው። ቀደም ሲል እንደተናገረው ፣ በስሱ የእንቅስቃሴ ዳሳሾች እና በተገለበጠ አዝራር ፣ ተንሸራታች ፍሎፕስ በሰዓት ጫፍ ላይ የግብዓት ምልክታችንን ብቻ ለማውጣት መቀርቀሪያዎችን ይጠቀማሉ። ይህ ቅደም ተከተል አመክንዮ ማለት የመንገድ መብራቶቻችን በፍጥነት እንቅስቃሴ ከተነዱ በኋላ ለተወሰነ ጊዜ ሊቆዩ ይችላሉ። ለ D-Flip Flop ኮድ መስጠቱ በጣም ቀላል ነው-

startprocess (CLK) የሚጀምር ከሆነ_ጅግ (CLK) ከዚያም ጥ <= D; ከሆነ ያበቃል; የማጠናቀቂያ ሂደት;

መግለጫው ከሆነ ነገሩ በሙሉ ወደ አንድ ሊጠቃለል ይችላል። አንዴ ይህንን ቁራጭ ከያዝን ፣ አራቱን አስፈላጊ የመገልበጥ ፍላፖችን የያዘ መዋቅራዊ የ VHDL ምንጭ ፋይል ፈጠርን-

DFF0 ን ይጀምሩ: የ DFF ወደብ ካርታ (CLK => CLK ፣ D => D (0) ፣ Q => ጥ (0)); DFF1: የ DFF ወደብ ካርታ (CLK => CLK ፣ D => D (1) ፣ ጥ => ጥ (1)); DFF2: የ DFF ወደብ ካርታ (CLK => CLK ፣ D => D (2) ፣ Q => ጥ (2)); DFF3: የ DFF ወደብ ካርታ (CLK => CLK ፣ D => D (3) ፣ ጥ => ጥ (3));

የባህሪ መጨረሻ;

ይህ ሁሉንም የስርዓት አካላት የበለጠ ንፁህ እና የተደራጁበት የእኛን ዋና መዋቅራዊ ፋይል ለማቆየት ይረዳል።

ደረጃ 4 - ሁኔታዎች

ኮዳችን የታመቀ እና ውጤታማ እንዲሆን ሁሉንም ቅድመ ሁኔታዎቻችንን በአንድ የጉዳይ መግለጫ ውስጥ ጽፈናል። ለዝቅተኛ ሞዴላችን እያንዳንዱ የእንቅስቃሴ ዳሳሽ ለ 4 ኤል.ዲ.:

case NMS “1111” => LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED <= "1111111111111111"; የመጨረሻ ጉዳይ;

ደረጃ 5: ገደቦች

ቪቫዶን በመጠቀም የእርስዎን ግብዓት እና ውፅዓት በትክክል ለመግለጽ ፣ ሁሉንም ወደቦች ፣ አዝራሮች ፣ ኤልኢዲዎች እና ሰዓቶች ጥቅም ላይ የሚውሉበትን የግዴታ ፋይል መተግበር አለብዎት።

set_property PACKAGE_PIN W5 [get_ports CLK] set_property IOSTANDARD LVCMOS33 [get_ports CLK]

set_property PACKAGE_PIN U16 [get_ports {LED [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [0]}] set_property PACKAGE_PIN E19 [get_ports {LED [1]}] set_property IOSTANDARD LVCMOS33 [get_ports] U19 [get_ports {LED [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [2]}] set_property PACKAGE_PIN V19 [get_ports {LED [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [3]}] set_property PAC get_ports {LED [4]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [4]}] set_property PACKAGE_PIN U15 [get_ports {LED [5]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [5]}] set_property PACKAGE_ LED [6]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [6]}] set_property PACKAGE_PIN V14 [get_ports {LED [7]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [7]}] set_property PACKAGE_PIN V13 8]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [8]}] set_property PACKAGE_PIN V3 [get_ports {LED [9]}] set_property IO STANDARD LVCMOS33 [get_ports {LED [9]}] set_property PACKAGE_PIN W3 [get_ports {LED [10]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [10]}] set_property PACKAGE_PIN U3 [get_ports {LED [11] [get_ports {LED [11]}] set_property PACKAGE_PIN P3 [get_ports {LED [12]}] set_property IOSTANDARD LVCMOS33 {LED [13]}] set_property PACKAGE_PIN P1 [get_ports {LED [14]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [14]}] set_property PACKAGE_PIN L1 [get_ports {LED [15]}] set_property IOSTANDARD LVCMOS [15]}]

set_property PACKAGE_PIN U18 [get_ports BTN] set_property IOSTANDARD LVCMOS33 [get_ports BTN]

set_property PACKAGE_PIN A14 [get_ports {MS [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [0]}] set_property PACKAGE_PIN A16 [get_ports {MS [1]}] set_property IOSTANDARD LVCMOS33 [get_ports] B15 [get_ports {MS [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [2]}] set_property PACKAGE_PIN B16 [get_ports {MS [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [3]}]

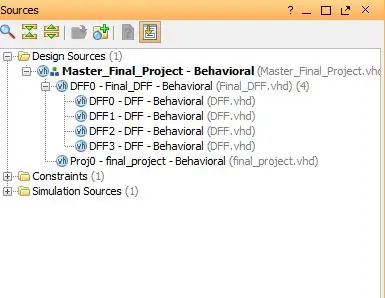

ደረጃ 6 ዋና ምንጭ ፋይል

በዚህ ዋና ፋይል ውስጥ ቀደም ሲል የተጠቀሱትን ሁሉንም የአካል ምንጭ ፋይሎችን አንድ ላይ እናመጣለን። ይህ ፋይል የተለያዩ አካላትን አንድ ላይ በማዋሃድ እንደ መዋቅራዊ ኮድ ይሠራል።

አካል Master_Final_Project Port (BTN: በ STD_LOGIC ፤ CLK: በ STD_LOGIC ፤ MS: በ STD_LOGIC_VECTOR (3 ወደ 0) ፤ LED: ከ STD_LOGIC_VECTOR (15 ወደ 0)) ፤ መጨረሻ Master_Final_Project;

አርቴክቸር የባህሪ_መጨረሻ_ፕሮጀክት ባህሪ ነው

ክፍል የመጨረሻ_ፕሮጀክት ወደብ ነው (--CLK በ STD_LOGIC ፤ ኤንኤምኤስ በ STD_LOGIC_VECTOR (3 ወደታች 0) ፤ ቢቲኤን በ STD_LOGIC ውስጥ--sw በ STD_LOGIC_Vector (1 ዳውን 0) ፤ LED: ከ STD_LOGIC_VECTOR (15 ወደ 0); የመጨረሻ ክፍል;

አካል Final_DFF ነው

ወደብ (CLK ፦ በ STD_LOGIC ፤ መ ፦ በ STD_LOGIC_Vector (3 ወደ 0) ፤ ጥ ፦ ከ STD_LOGIC_Vector (3 እስከ 0)) ፤ የመጨረሻ ክፍል;

ምልክት DFF02proj30: STD_LOGIC;

ምልክት DFF12proj74: STD_LOGIC; ምልክት DFF22proj118: STD_LOGIC; ምልክት DFF32proj1512: STD_LOGIC;

ጀምር

DFF0: Final_DFF ወደብ ካርታ (CLK => CLK ፣ D (0) => MS (0) ፣ D (1) => MS (1) ፣ D (2) => MS (2) ፣ D (3) => MS (3) ፣ ጥ (0) => DFF02proj30 ፣ ጥ (1) => DFF12proj74 ፣ ጥ (2) => DFF22proj118 ፣ ጥ (3) => DFF32proj1512); Proj0: final_project ወደብ ካርታ (NMS (0) => DFF02proj30 ፣ NMS (1) => DFF12proj74 ፣ NMS (2) => DFF22proj118 ፣ NMS (3) => DFF32proj1512 ፣ BTN => BTN ፣ LED => LED); የባህሪ መጨረሻ;

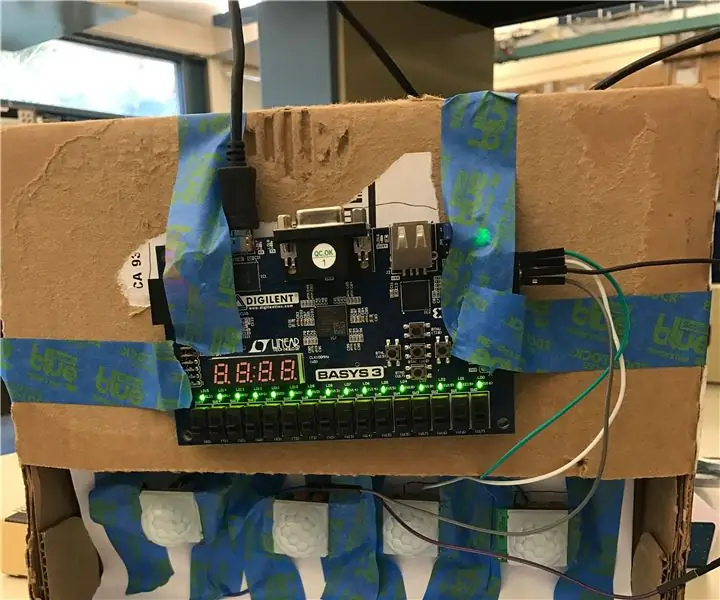

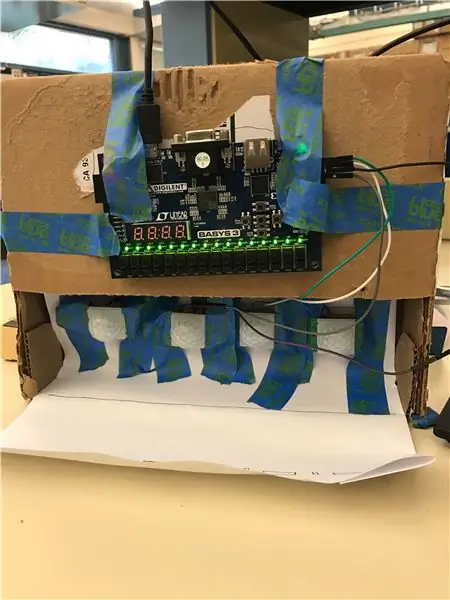

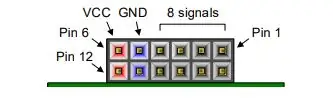

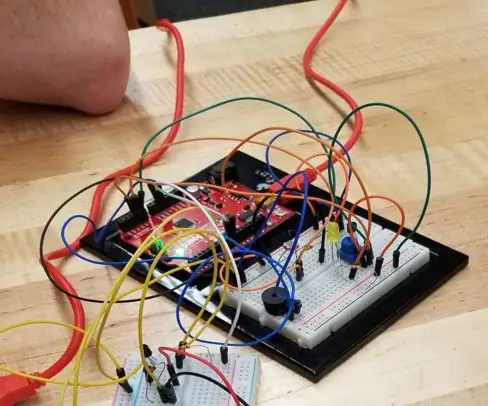

ደረጃ 7 - ስብሰባ

ለዚህ ፕሮጀክት የሃርድዌር ስብሰባ አነስተኛ ነው። የሚፈለጉት ቁርጥራጮች እንደሚከተለው ናቸው

1. Basys 3 ሰሌዳ (1)

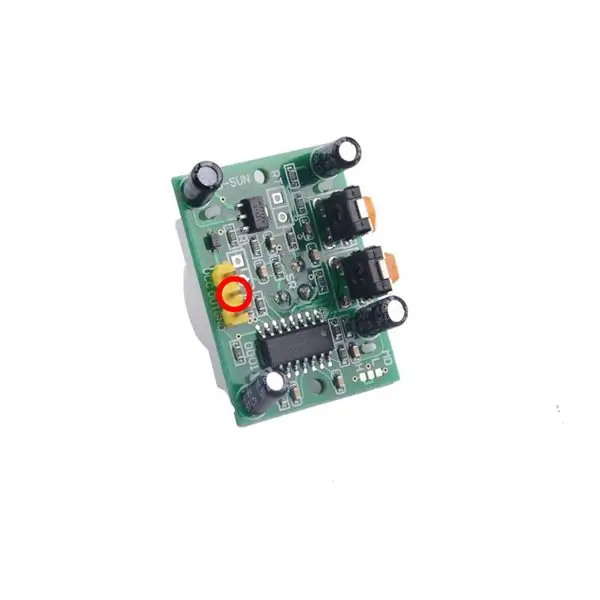

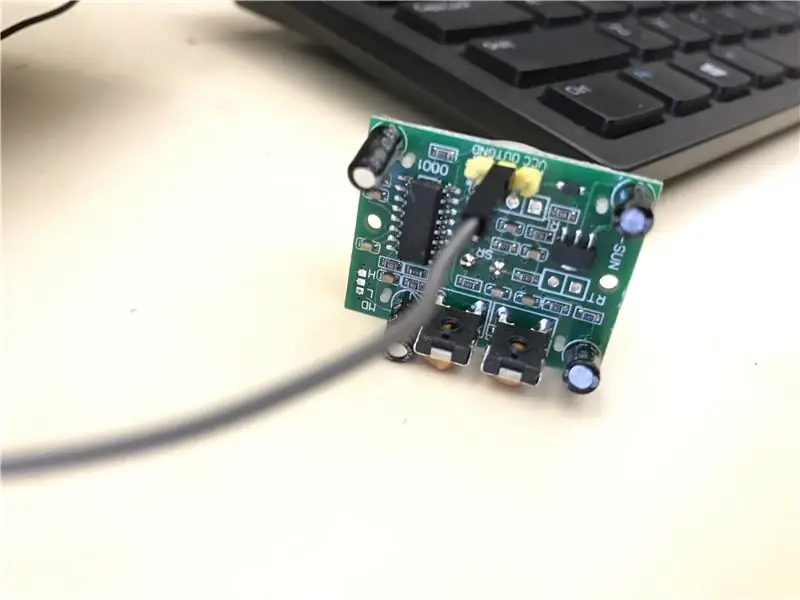

2. እዚህ በአማዞን ላይ ሊገኙ የሚችሉ ርካሽ የእንቅስቃሴ ዳሳሾች። (4)

3. ከወንድ ወደ ሴት የሚመራ (4)

ስብሰባ

1. 4 ወንድ መሪዎችን ወደ PMod ራስጌ JB ወደቦች 1-4 ያገናኙ (ምስል ይመልከቱ)።

2. የሴት ጫፎችን ከእያንዳንዱ የእንቅስቃሴ ዳሳሽ የውጤት ፒን ጋር ያገናኙ።

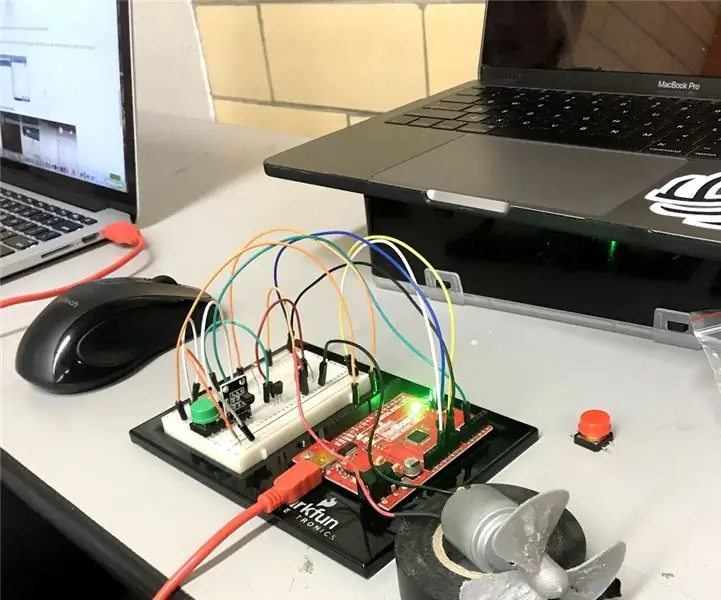

ደረጃ 8 - ፕሮግራሙን በመጫን ላይ

አሁን የ VHDL ዋና ምንጭ ፋይልን ወደ Basys 3 ሰሌዳ ለመጫን ዝግጁ ነን። ለማንኛውም ሊሆኑ የሚችሉ ስህተቶች ውህደት ፣ ትግበራ እና የትንሽ ፍተሻ መፈተሽን ያረጋግጡ። ሁሉም በተሳካ ሁኔታ ከሄዱ የሃርድዌር አስተዳዳሪውን ይክፈቱ እና የ Basys 3 መሣሪያን ያቅዱ። የእርስዎ ፕሮጀክት አሁን ተጠናቅቋል!

የሚመከር:

የአልትራሳውንድ ዳሳሽ በመጠቀም ራስ -ሰር የመንገድ መብራቶች 3 ደረጃዎች

የአልትራሳውንድ ዳሳሽ በመጠቀም ራስ -ሰር የመንገድ መብራቶች -የመንገድ መብራቶች በሌሊት በራስ -ሰር እንዴት እንደሚበሩ እና ጠዋት ላይ በራስ -ሰር እንደሚጠፉ አስበው ያውቃሉ? እነዚህን መብራቶች ለማብራት/ለማጥፋት የሚመጣ ሰው አለ? የመንገድ መብራቶችን ለማብራት ብዙ መንገዶች አሉ ግን የሚከተለው ሐ

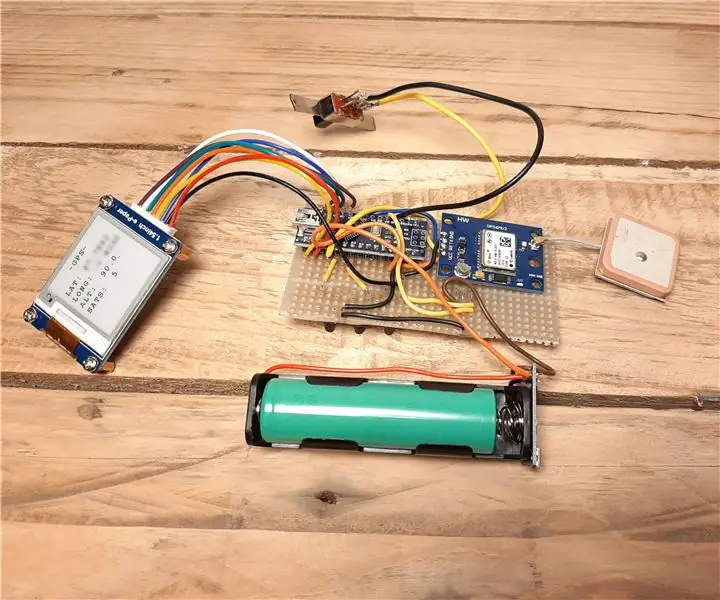

በኢ-ኢንክ ማሳያ አማካኝነት ኃይል ቆጣቢ ጂፒኤስ -4 ደረጃዎች

በኢ-ኢንክ ማሳያ አማካኝነት ኃይል ቆጣቢ ጂፒኤስ:-በበጋ በየሩቅ ቦታዎች በእግር እጓዛለሁ። አንዳንድ ጊዜ ፣ ዱካው ሲደክም አልፎ ተርፎም ሲጠፋ ፣ መጋጠሚያዎቼን ለማግኘት ስልኬን ጂፒኤስ መጠቀም አለብኝ እና ከዚያም በወረቀት ካርታ ላይ ያለኝን ቦታ መፈተሽ አለብኝ (ብዙውን ጊዜ ምልክት የለኝም ስለዚህ የወረቀት ካርታዎች አስገዳጅ ናቸው

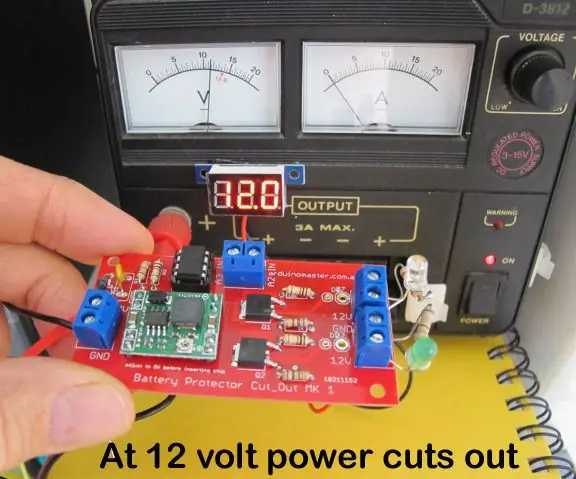

የባትሪ ኃይል ቆጣቢ ፣ የፍሳሽ መከላከያ ተቆርጦ መቀየሪያ በ ATtiny85 ለሊድ አሲድ መኪና ወይም ለሊፖ ባትሪ 6 ደረጃዎች

የባትሪ ኃይል ቆጣቢ ፣ የፍሳሽ መከላከያ ተቆርጦ መቀየሪያ በ ATtiny85 ለሊድ አሲድ መኪና ወይም ለሊፖ ባትሪ-ለመኪናዎቼ እና ለፀሃይ ሥርዓቶቼ በርካታ የባትሪ መከላከያዎች ስለሚያስፈልጉኝ የንግድ ሥራዎቹን በ 49 ዶላር በጣም ውድ ሆኖ አግኝቼዋለሁ። እንዲሁም በ 6 mA በጣም ብዙ ኃይል ይጠቀማሉ። በጉዳዩ ላይ ምንም መመሪያ ማግኘት አልቻልኩም። ስለዚህ 2 ኤምኤ የሚስበው የራሴን ሠራሁ። እንዴት ነው

የአርዱዲኖ የቤት ኃይል ቆጣቢ 5 ደረጃዎች

አርዱዲኖ የቤት ኃይል ቆጣቢ - የኤሌክትሪክ እና ሌሎች የፍጆታ ሂሳቦችን ለመቀነስ የቤትዎን ኃይል ለመቆጣጠር የታሰበ የቤት ኃይል ስርዓት እየገነቡ ነው። በዚህ ሞዴል ውስጥ መሣሪያዎ የቤትዎን የሙቀት መጠን ለመፈተሽ እና በዚህ መሠረት ለማስተካከል ይችላል

ፕሮጀክት የቤት ኃይል ቆጣቢ 8 ደረጃዎች

ፕሮጀክት የቤት ኃይል ቆጣቢ ሃና ሮቢንሰን ፣ ራሔል ዊየር ፣ ካይላ ክሌሪ የአርዱዲኖ ቦርድ እና ማትላብ አጠቃቀም የቤት ባለቤቶችን የኃይል አጠቃቀምን እንዲያሻሽሉ ለመርዳት ቀላል እና ውጤታማ ዘዴ መሆኑን አረጋግጧል። የአርዱዲኖ ቦርድ ቀላልነት እና ሁለገብነት አስገራሚ ነው። አሉ